基于FPGA的超高速雷达信号实时采集存储系统

宋 杰, 何 友, 唐小明

海军航空工程学院 信息融合技术研究所, 山东 烟台264001

摘 要: 采用服务器作为采集主控设备,利用多个硬盘组成磁盘阵列作为存储设备,并制作了一块基于FPGA的超高速雷达信号采集PCI卡。系统以FPGA为采集的核心控制芯片,并在FPGA内部实现了64位/66MHz的PCI接口逻辑,无需专用接口芯片,简化了电路板设计,提高了系统的灵活性。该系统数据传输总速率可高达528MB/s,实时流盘速度可达150MB/s,存储容量可扩展至1000GB以上。

关键词: FPGA 超高速 实时 数据采集 数据存储

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达1000万门;全部控制逻辑由硬件资源完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

实时流盘一直是数据采集技术的最大瓶颈,它直接制约了采集存储设备的实时存储能力。为此,可考虑利用多个硬盘组成RAID阵列(廉价冗余磁盘阵列)[1~2]。RAID的初衷主要是为大型服务器提供高端的存储功能和冗余的数据安全。RAID把多块独立的硬盘(物理硬盘)按不同方式组合起来形成一个硬盘组(逻辑硬盘),从而提供比单个硬盘更高的存储性能,提供数据冗余的技术。

1 总体方案

本文设计并实现了一种超高速的雷达信号采集存储系统,其工作原理框图如图1所示。

本系统采用服务器作为采集主控设备,利用多个硬盘组成磁盘阵列作为存储设备。从以前的使用情况看,在普通主板上集成RAID控制器,采用IDE硬盘组成RAID0阵列情况下,磁盘阵列实测的读写速度可达40MB/s;在使用SCSI硬盘和Adaptec公司的RAID卡情况下,实测速度可达70MB/s;在使用SATA硬盘和3WARE公司的RAID卡情况下,实测速度可达150MB/s,且最新的SATA硬盘容量大、价格便宜;若采用12个160GB的SATA硬盘,则容量能达到惊人的1920GB。无论从性能上还是从价格上,采用SATA硬盘组成SATA RAID磁盘阵列都是一种比较理想的选择。

由于采用64位/66MHz接口的PCI卡,其总线数据传输速率为普通32位/33MHz接口的PCI卡的四倍,总速率可高达528MB/s。此方案比较适合超高速雷达信号的实时采集与实时存盘,采用RAID磁盘阵列后流盘速度得到了较大的提高,明显改善了数据传输与数据存盘之间速度不匹配这一瓶颈问题。

2 硬件设计

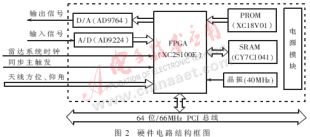

系统硬件总体设计考虑到系统的通用性、可扩展性以及数据传输、终端处理的需要,选用通用64位/66MHz的PCI局部总线与主机(服务器)进行实时数据交换,有利于实现系统的模块化设计和集成,提高了数据的灵活处理能力。PCI插卡实际硬件结构如图2所示。

FPGA采用Xilinx(赛灵思)公司的10万门FPGA芯片XC2S100E,其配置芯片为Xilinx公司的1Mbits容量PROM芯片XC18V01,以主动串行方式对FPGA进行上电配置。AD、DA分别为ADI(模拟仪器)公司12位高速模数转换芯片AD9224与14位高速数模转换芯片AD9764。SRAM采用Cypress Semiconductor(塞普拉斯半导体)公司的256K×16bits SRAM芯片CY7C1041。

设计中利用FPGA实现64位/66MHz的PCI接口逻辑,进行实时信号采集和传输控制。由于FPGA具有层次化的存储器系统,其基本逻辑功能块可以配置成16×1、16×2或32×1的同步RAM,或16×1的双端口同步RAM,因此可以在FPGA内部配置高速双口RAM作为信号传输的数据缓冲器。同时,为了节省FPGA的内部逻辑资源,在FPGA外围配置了适当的SRAM用来存储数据。

3 软件设计

3.1 FPGA程序设计

3.1.1 FPGA内部功能模块分析

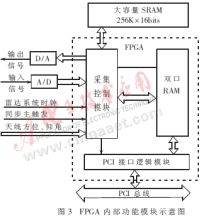

FPGA内置多个功能部件,主要包括雷达信号采集控制模块与PCI接口逻辑模块。FPGA内部功能组成原理图如图3所示。

FPGA作为系统总的控制枢纽,参与了系统具体任务的实现。内部功能模块的工作过程为:首先采集控制模块通过对AD转换电路的时序控制将雷达视频信号转换成数字信号并暂存于FPGA内部双口RAM中,然后再将双口RAM中的数据通过PCI接口逻辑模块送往计算机。

3.1.2 采集控制模块程序设计

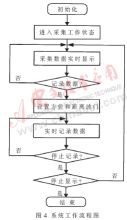

本系统要求能够在普通显示器上对采集的雷达视频回波信号进行长时间的实时显示。同时在显示过程中,可对任意区域设置采集方位和距离波门,将采集的数据实时存储在磁盘阵列上。系统工作流程如图4所示。

采集卡与计算机之间的数据交换以FPGA内部配置的高速双口RAM作为数据传输的缓冲器,采用两片双口RAM乒乓切换的方式进行数据传输[3]。具体方法为:在FPGA内部配置两片8K×32bits的双口RAM,采集开始时,将采集数据往第一片双口RAM中写,当第一片双口RAM写满时,采集控制模块产生乒乓切换信号,数据自动存入第二片双口RAM中,同时以DMA方式将第一片双口RAM中的采集数据传送给计算机,如此轮换交替。这样DMA传输和接收A/D数据可以同时进行,而DMA的速率远大于A/D采集速率,从而有效地避免数据丢失。

3.1.3 PCI接口逻辑模块程序设计

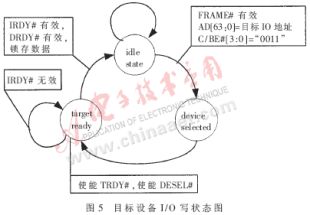

为了实现PCI总线各控制信号间的时序关系,可以根据具体的交易设计相应的状态机。以目标设备I/O写为例:当帧有效信号(FRAME#)有效(低电平)时标志着一次交易的开始,C/BE#[3:0]为“0011”表明此交易为I/O写,同时AD[63:0]上的数据为此次交易的I/O地址。如果此I/O地址与设备配置寄存器中I/O基地址寄存器(Base Address Register)的值相同,目标设备通过使DESEL#有效来声明这次交易。作为主设备,在FRAME#、I/O地址和C/BE#有效后在AD[63:0]上驱动要传输的数据、在C/BE#上驱动字节使能、同时使能目标准备好信号IRDY#,直到检测到目标设备有效的DRDY#信号,此次交易中的主设备和目标设备停止驱动各种信号。而目标设备在准备好接收数据后就可以使能DRDY#,此后目标设备检测到IRDY#时可以根据具体的字节使能C/BE#[3:0]将AD[63:0]总线上的数据进行锁存,从而完成整个交易[4]。此交易的状态图如图5所示。

本系统利用VHDL编程在FPGA中实现了64位/66MHz的PCI接口逻辑,其中实现的功能包括:配置空间读写、目标设备I/O映射与内存映射端口读写和主设备DMA控制。实际调试中,DMA传输的瞬时传输速率可达132Mbps,其连续传输速率也可达100Mbps。

3.2 驱动程序设计

3.2.1 DriverWorks生成驱动程序框架

NuMega公司的Driver Studio是一套为简化Windows应用程序和设备驱动程序的开发、调试及测试工具包。其中有WDM和WINNT的驱动程序开发软件DriverWorks、Windows操作系统内核模式调试软件SoftICE和开发Win9X(Windows95和Windows98)的虚拟设备驱动程序(VxD)的VToolsD。

DriverWorks以面向对象(OOP)的方式,将编写WDM及WINNT驱动程序所需的对内核模式访问及硬件的访问封装成类。DriverWorks是基于VC++的,它生成标准的VC工程,只要将所建的工程在VC下编译,就可以生成最终的设备驱动程序。

3.2.2 VC++二次开发设备驱动程序

DriverWorks向导生成了两个类:一个是设备驱动程序类,另一个是设备对象类。驱动程序类主要完成WDM的DriverEntry和AddDevice例程。设备对象类就是与硬件对应的功能设备对象(FDO)类,与硬件交互的例程都是针对此类的。

DriverWorks生成驱动程序框架,根据具体功能,用户还需在VC++工程下添加自己的代码。常用的功能有:IO映射端口访问、内存映射端口访问和中断处理。DriverWorks将编写WDM驱动程序所需的对内核模式访问及硬件的访问封装成类,其中,KPciConfiguration类用于实现对PCI设备配置空间的访问,KIoRange 类用于实现对I/O映射端口的访问,KMemoryRange 类用于实现对内存映射端口的访问,KDmaAdapter、KDmaTransfer和KCommonDmaBuffer类用于实现DMA操作,Kinterrupt类用于实现中断处理操作。

3.3 应用程序设计

3.3.1 应用程序与驱动程序之间的通信[5]

在Windows中,应用程序实现与WDM通信的过程是:应用程序先用CreateFile函数打开设备,然后用DeviceIoControl与WDM进行通信,包括从WDM中读数据和写数据给WDM两种情况,当应用程序退出时,用CloseHandle关闭设备。

驱动程序有时需要主动通知上层应用程序执行某个操作,以实现硬件响应的实时性。这可以通过在应用程序中创建一个事件,将该事件句柄放入输入缓冲区中,通过函数DeviceIoControl传给驱动程序,并创建一个线程来守候该事件被激活。

3.3.2 用户界面程序设计

用户程序主要完成雷达视频信号的采集参数设置、采集数据的实时显示和实时存盘。采集工作过程如下:首先通过用户程序对采集参数进行设置并通过计算机PCI接口发往PCI卡的FPGA中,FPGA则根据这些参数控制雷达视频信号的采集;然后用户可以点击“开始”按钮启动采集过程,可以在P显和A显坐标下观察采集的目标回波信号,同时将采集的雷达回波数据以二进制格式实时保存在磁盘阵列上,供Matlab等软件进一步分析使用。

目前,本系统已对某型舰载警戒搜索雷达成功地进行了实际外场数据采集。图6为P显和A显坐标下采集到的真实雷达视频回波信号。实验表明这个系统完全满足所提出的指标要求,能够做到大容量高速连续采集,且稳定可靠,测得的数据能够真实地反映目标与环境的特性,可用于检验各种目标检测、识别、跟踪算法。

本系统还可用于超高速雷达信号处理机中,利用大容量FPGA可直接对AD转换后的雷达中频信号进行高速实时处理,处理结果可通过PCI总线高速传输到计算机内存中,同时利用高速、大容量磁盘阵列进行实时的海量数据存盘。

参考文献

1 周 骞,陈金树. 超高速数据采集存储系统的设计与实现. 计算机应用研究, 2003;(8)

2 李 军,孙朋举. 基于高速磁盘阵列的数据采集系统及其应用. 舰船电子对抗, 2002;(6)

3 付 强, 刘 阳.雷达目标回波数据采集系统的设计与实现.系统工程与电子技术, 1995;(9)

4 Tom.Shanley, Don.Aderson著, 刘 晖译. PCI系统结构(第四版).北京:电子工业出版社, 2000

5 武安河. Windows2000/XP WDM设备驱动程序开发.北京:电子工业出版社, 2003

010-62156134 62169728 13301007825 节假日:13901042484 微信号:sun62169728

地址:北京市西城阜外百万庄扣钟北里7号公寓

E_mail:sales@pc17.com.cn 传真: 010-68328400

京ICP备17023194号-1 公备110108007750